# <u>ארכיטקטורת מחשבים</u>

# שיעור 1: 1. מגמות בשימוש במחשבים ובטכנולוגיות:

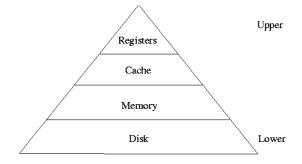

כשמגדירים Instruction Set צריך לקחת בחשבון את העלייה בזיכרון שבו משתמשות התוכניות. במערכות מחשב נחוצות 3 טכנולוגיות בסיסיות:

- 1. גדלים במהירות transistor count- וה-devices מהירות מהירות transistor count גדלים במהירות.

- באופן איטי מאוד. cycle time :Semiconductor DRAM .2

- 3. טכנולוגיות דיסק מגנטי: disk density גדלה במהירות. זמן גישה משתפר באיטיות.

### 2. ביצועי המחשב:

בכל שושים בכל BogoMips מדרג את מהירות המע' – *כמה פעולות עושים בכל BogoMips:* מידה של ביצועים במע' Linux. ה-BogoMips מדרג את מהירות המע'

$$(1) \frac{MHz}{BogoMips} = CPI$$

<u>המטרה:</u> הקטנת ה-response time של המחשב.

(2)

$$\frac{ExTime(Y)}{ExTime(X)} = \frac{Performance(X)}{Performance(Y)}$$

#### :Amdahl חוק

חוק Amdahl משמש להערכת השיפור בביצועים כתוצאה משימוש במצב ביצוע אחר לביצוע תת קבוצה של פונקציונליות מע' המחשב.

. היחס של הביצועים (performance) לאחר השיפור לעומת הביצועים לפני השיפור (speedup

הזמן של החלק שאני רוצה לשפר (לפני השיפור).  $T_{e}$

החלק היחסי בזמן הביצוע של החלק אותו נרצה לשפר במכונה המקורית.  $F_e$

.enhanced execution-השיפור עקב ביצוע ה: $S_e$ : זמן הביצוע המקורי.

. זמן הביצוע החדש: $T_{new}$

(4)

$$T_{new} = T_{old}((1 - F_e) + \frac{F_e}{S_e})$$

(5) Speedup =

$$\frac{T_{old}}{T_{new}} = \frac{1}{(1 - F_e) + \frac{F_e}{S_e}}$$

:סה"כ זמן CPU של תוכנית

(6)

$$T_{CPU} = \frac{CPU \ Cylces}{Clock \ Rate} = (CPU \ Cycles) \cdot (Clock \ Cycle \ Time)$$

(7)

$$T_{CPU} = \frac{IC \times CPI}{Clock \ Rate} = IC \times CPI \times Clock \ Cycle \ Time$$

כלומר, עמ"נ לשפר את הביצועים צריך להגדיל את אחד הגורמים במשוואה (6).

(8) CPU Cycles =

$$\sum_{i=1}^{n} CPI_{i} \times IC_{i}$$

### <u>דוגמה:</u>

. Speedup = 1 מקבלים לא משפרים שום דבר אם , Se = 1 אם , Se = 1

. יהיה אינסופי Speedup-אם אומר בחינם, אומר משהו לעשות משהו לעשות משהו לעשות משהו אומר אומר אומר אינסופי.

### שימוש נוסף לנוסחת Amdahl: מעבדים מקבילים:

אם יש כמה בעיות שניתן לעשות במקביל וכמה שניתן לבצע סדרתית, ניתן לעשות Speedup רק לחלק שניתן לעשות במקביל. במקרה זה:

. החלק היחסי של הבעיה שהוא מקבילי:  $F_e$

. מספר המעבדים שמוסיפים: $S_e$

מה כדאי לשפר כדי להקטין את זמן הביצוע?

| Clock Rate | CPI | Instruction Count |                 |

|------------|-----|-------------------|-----------------|

|            |     | X                 | תוכנית          |

|            | X   | X                 | מהדר            |

|            | X   | X                 | Instruction Set |

| X          | X   |                   | ארגון           |

| X          |     |                   | טכנולוגיה       |

# שיעור 2: 1. ארכיטקטורת DLX

מחשב עם פעולות מסובכות: מאופיין בפקודות מחשב קצרות, פעולות של מחרוזות, סט פקודות עשיר *:CISC*: מרשב עם פעולות מסובכות: מאופיין בפקודות מחשב קצרות, פעולות של מחרוזות, סט פקודות עשיר (VAX). בע*ירה:* ביצועים,

#### :RISC

ל-DLX יש 3 סוגי פקודות. כל פקודה היא בגודל אחיד – 32 ביטים ← פענוח מהיר.

. ביטים ע"י 5 ביטים ביטים.  $\dot{3}$  מספר האוגרים הוא די גדול

התחלת פקודה היא תמיד <u>כפולה של 4</u>. כל ה-data נכתב/נקרא מהזיכרון בכפולה טבעית (כפולה של 4).

I-Type Instruction:

| 1 Type Institute |    |    |    |    |    |    |           |

|------------------|----|----|----|----|----|----|-----------|

| 31               | 26 | 25 | 21 | 20 | 16 | 15 | 0         |

| OP-Code          | 2  | rs | S  |    | rd |    | immediate |

R-Type Instruction:

| 31  | 26   | 25 | 21 | 20 | 16 | 15 | 11 | 10  | 6  | 5 | 0   |

|-----|------|----|----|----|----|----|----|-----|----|---|-----|

| OP- | Code | rs |    |    | rt |    | rd | sha | mt | i | unc |

J-Type Instruction:

|    | <i>7</i> 1 |             |

|----|------------|-------------|

| 31 | 26         | 25 0        |

|    | OP-Code    | jump offset |

#### פקודות לדוגמה:

Data Transfer: lb, lh, lw, ld, sd, movd.

ALU Instructions: add, addi, addui, sub, mult, div, and, or, xor, lhi, sll, srl, sra, seq, sne, slt, sgt.

Control Instructions: beqz, bnez, j, jr, jal, jalr, trap, rfe.

FP Instructions: addd, addf, subd, divd, multd, multf, cvtd2f, cvtf2d, eqd, ltd, led.

lw r5, o(r3) // r5  $\leftarrow$  addr[r3 + offset].

sw 8(r3), r5 // [r3 + 8]  $\leftarrow$  r5.

<u>דוגמה:</u>

int a[5], \*pa;

pa = &a[2]; // 4 המצביע הוא תמיד כפולה של

\*pa = 5;

pa = 2 + (char \*)&a[2]; // 4ב-2 ולא ב-2 ולא ב-2 כעת המצביע מתחלק

\*pa = 5; // segmentation – מנסים להשתמש במצביע ולכן עפים

העובדה שהפקודות הן aligned חוסכת בסיבוכיות. שובדה שהפקודות הן unaligned מאפשר גם Intel

*nop:* בד"כ מופיע אחרי RISC .branch/jump בד"כ עובדים על pipeline בד"כ מופיע אחרי אחרי בדיך להכניס בד"כ עובדים על branch צריך להגיע לקטע אחר בתוכנית, אולם ה-branch צריך להגיע לקטע אחר בתוכנית, אולם ה-branch מלא בדברים אחרים. לכן משתמשים ב-nop ישר אחרי ה-branch כדי לא להגיע למקומות שלא רצינו.

<u>עמ' 4 – שיעור 2 – מבנה ה-Datapath</u>

$\underline{V}$ עמ'  $\underline{V}$  – שיעור  $\underline{V}$  – תרגום תוכנית  $\underline{V}$  לאסמבלר – שיעור 2

# שיעור 3: ארכיטקטורת DLX

Datapath - 3 עמ' 2 - 2

.cycles 5 של ה-DLX מאפשר לכל פקודה להתבצע לאחר 4 או DLX ה-datapath של ה-מבעל מאפשר לכל פקודה לפעימות שעון.

#### יש 5 שלבים:

|       |                                    |                                         |                        |                | .0000                      |

|-------|------------------------------------|-----------------------------------------|------------------------|----------------|----------------------------|

| Stage | Memory Reference                   | Register – Register A                   | LU                     | Register – Imm | Branch                     |

|       |                                    |                                         |                        | ALU            |                            |

| IF    |                                    | IR ← N                                  | IEM[PC]                |                |                            |

|       |                                    | NPC <del>&lt;</del>                     | -PC+4                  |                |                            |

| ID    |                                    | A ← Reg                                 | s[IR <sub>2125</sub> ] |                |                            |

|       |                                    | B ← Reg                                 | $s[IR_{16,,20}]$       |                |                            |

|       |                                    | $Imm \leftarrow ((IR_{16}) \# \#^{16})$ |                        | n extension    |                            |

|       |                                    |                                         | 0,,15                  | ,              |                            |

| EX    | ALUOut ← A + Imm                   | ALUOut ← A func B                       | ALUOU                  | JT ← A op Imm  | ALUOUT ← NPC + Imm         |

|       |                                    |                                         |                        |                | Cond $\leftarrow$ A op 0   |

| MEM   | (for loads)                        |                                         |                        |                | if (cond)                  |

|       | $LMD \leftarrow Mem[ALUOut]$       |                                         |                        |                | PC ← ALUOut                |

|       | (for stores)                       |                                         |                        |                | else                       |

|       | Mem[ALUOut] ← B                    |                                         |                        |                | PC ← NPC                   |

|       |                                    |                                         |                        |                | עבור branch עם cond עוברים |

|       |                                    |                                         |                        |                | לפלט של ה-ALU (הפקודה      |

|       |                                    |                                         |                        |                | הבאה המחושבת).             |

|       |                                    |                                         |                        |                | NPC = PC + 4אחרת ל         |

| WB    | (for loads)                        | $Regs[IR_{11,,15}] \leftarrow ALUOut$   | Regs[IR <sub>16</sub>  | ,,20] ← ALUOut |                            |

|       | $Regs[IR_{16,,20}] \leftarrow LMD$ | -                                       |                        |                |                            |

. קריאת הפקודה מהזיכרון:  $Instruction\ Fetch-IF$

. שליפת הערכים מהאוגרים: Instruction Decode / Register Fetch – ID

. ביצוע פעולות אריתמטיות: Execute / Address Calculation – EX

. כתיבה/קריאה לזיכרון:  $Memory\ Access - MEM$

. כותבים אוגר :Write Back – WB

#### :Pipelining :4

pipelining doesn't help latency of a single task, it helps throughput of an entire workload.

<u>:Pipeline – 3 שיעור</u> – <u>שיעור</u>

<u>Pipeline:</u> יצירת חפיפה בין דברים במהלך הביצוע. לוקחים את מה שלוקח הכי הרבה זמן וזו תהיה היחידה הבסיסית

.RT זה לא טוב עבור ← latency *חסרון:*

יגדל. throughput-יתרון: ה

בכל מלבן (latch) שומרים הנתונים המקומיים הנוכחיים והם זורמים מאחד לשני. הפלט של ה-*latch* קבוע. ברגע שיש אירוע (סוף פעימת שעון) אזי הקלט באותו רגע נהפך לפלט ועד סוף פעימת השעון הקלט לא משתנה.

.superscalar בתוך ה-chip יהיה יותר מ-ALU אחד

#### :Hazards

<u>:Hazards – 3 שיעור – 5-4</u>

ב-pipeline אידיאלי בלי hazards הכל עובר חלק ולכן בממוצע תתבצע פקודה אחת כל פעימת שעון אחת.

# <u>3 סוגי מכשולים:</u>

1. מבני (Structural):

כאשר יש זיכרון משותף לנתונים ולפקודות  $\leftarrow$  *Structural Hazard*, שכן בכל פעימת שעון צריך לקרוא פקודה (data תפוס ובפעימת השעון ה-4 יש גישה לזיכרון (קריאת  $\leftarrow$  memory port) בכל פעימת שעון ה-1 היש הואין מספיק משאבים באותה פעימת שעון כדי לבצע את הפעולה.

פתרון: stalls: נשהה את ביצוע הפקודה ה-4 כל פעם בפעימה אחת.

הפתרון עובד שכן רק כ-20% מהגישות לזיכרון הן לכתיבה, ואילו בשאר הפעמים הגישה היא רק לקריאה. store מול load מול store וזה מתבצע רק בכ-20% מהפקודות.

. במחשב שלנו המכשול הזה לא קורה בד"כ בגלל שיש cache נפרד לנתונים ולפקודות.

# 2. נתונים (data):

.Data Hazard ← כאשר צריך להשתמש בערך של אוגר לפני שהערך הזה חושב

לדוגמה

add r1, r2, r3 // the value of r1 is computed at the  $3^{rd}$  cycle, but only written in the  $5^{th}$  cycle (WB). sub r4, r1, r3 // need to use r1 in the  $3^{rd}$  cycle.

# <u>Data Hazards – 4 שיעור – 3-1</u>

נשים לב שהערך של r1 ידוע כבר בסוף הפעימה ה-3, אולם הוא עוד לא נכנס לתוך האוגר – הערך שלו עוד ב-ALU. ניתן לקצר את ה-ALU.

הפעימה ניתן לקרוא את הערך של ה-ALU נכנס ל-mux נכנס ל-ALU הפלט של ה-forwarding (פתרון: stalls הפעודכן (פתרון ללא און לקרוא את הערך המעודכן המעודכן (פתרון לקרוא את הערך המעודכן המע

הפתרון טוב עבור חישובים אריתמטיים באוגרים, אולם לא עבור פקודות load. למשל:

lw r1, 0(r2) // the value of r1 is known at the end of the 4<sup>th</sup> cycle.

sub r4, r1, r3 // the value of r1 is needed at the beginning of the 3<sup>rd</sup> cycle.

שכן forwarding בפעימה ה-3. אי אפשר לפתור את זה ע"י פקודת ALU כאן r1 נוצר רק בפעימה ה-4 ולא ע"י פקודת הוא נחוץ.

פתרון: stall של פעימת שעון אחת עבור כל הפקודות.

#### עמ' 4-3 – שיעור 4 – Control Hazards

.4- הבדיקה האם התנאי לקפיצה מתקיים או לא נעשית רק בפעימה ה-4. branch יש פקודת: branch. הבדיקה האם התנאי לקפיצה מתקיים או לא נעשית רק בפעימה ה-4. מה עושים עד אז? מחשבים כרגיל את שאר הפקודות? שמים

פ*תרון 0:* נעשה השהייה עד שנדע לאן צריך לקפוץ.

<u>פתרון 1:</u> "מנחשים" שה-branch לא מתקיים (predict branch not taken) ולכן ממשיכים את הביצוע הרגיל. אם בזמן הבדיקה של ה-branch רואים שהוא צריך להתקיים אזי מפסיקים את הביצוע של הפקודות, ומבצעים את בזמן הבדיקה של ה-branch (delay slot כיוון שבפעימה ה-3 נדע אם צריך לקפוץ או לא, אזי אם צריך לקפוץ נבטל את הקפיצה (אין כאן theline). כיוון שבפעימה ה-3 נדע אם ב-pipeline שכן אף נתון עוד לא נכתב, עוד לא שינינו שום הפקודות שביצענו – בעצם צריך לבטל רק את מה שב-pipeline שכן אף נתון עוד לא נכתב, עוד לא שינינו שום דבר (שכן עוד לא היה Write Back אוגר 0 (שקול ל-nop). אבל לעומת זאת, הפסדנו 3 פעימות שעון.

stall אזי הפסד של 3 פעימות שעון כל פעם מכניס בעצם branch כיוון שבממוצע כל פעולה חמישית/שישית היא stall אזי הפסד של 5 פעימות שעון כל פעם מכניס בעצם stalls בפועל לתוכניות. נרצה להקטין את מספר ה-stalls שנובעים מ-branch

### 2 פתרונות:

- 1. **שינוי במחשב:** מוסיפים ALU נוסף שתפקידו: לחשב את יעד הקפיצה (PC + 4) + offset) כעת, במקום לחכות ALU נוסף שתפקידו: לחכות Branch מצליח אזי יש רק השהייה של פעימת שעון נחכה רק פעימה אחת. אם ה-branch מצליח אזי יש רק השהייה של פעימת שעון אחת. *חסרון:* פתרון מסובך ודורש יותר חומרה.

- 2. ממיד מבצעים פעולה, שבין כה וכה צריך לבצע, ישר אחרי RISC ברוב מחשבי *branch delay slot.* ה-branch

# ביטה נוספת: ננחש אם צריך לקפוץ לפי ה-branch target address cache:

מבנה ה-cache:

|                  | ieaene ii iia |

|------------------|---------------|

| address          | target        |

| הכתובת של הפקודה | החישוב        |

ברגע שרואים branch בודקים אם ה-pc מופיע ב-cache ואם כן יודעים מה כתובת הקפיצה (לפי ה-cache) ולא צריך לחשב עוד פעם.

לרוב, חוזרים על לולאות ולכן זוכרים את ה-branch ולא צריך לחשב כל פעם מחדש.

cache שבו זוכרים מה עשית בפקודה הזו בפעם האחרונה. ההנחה היא שבאופן cache שבו זוכרים מה עשית בפקודה הזו בפעם האחרונה. מטטיסטי יש התאמה בין אם קפצת בפקודה הזו קודם ובין אם תקפוץ בה עכשיו ולפי זה נבחר predict taken או predict untaken.

ב*פנטיום* זוכרים היסטוריה של יותר מפקודה אחת.

# :Exceptions :5

.pipeline במהלך התוכנית בארכיטקטורה עם exceptions-

exceptions: אם ה-exceptions גורמות לכל הפקודות שלפני הפקודה שגרמה ל-exceptions להסתיים exceptions אולם כל הפקודות שלאחר הפקודה הנ"ל לא תושלמנה. [ניתן לשחזר במדויק מה שהיה]

mprecise exceptions לא מתקיימת (למשל: במחשבי imprecise exceptions). (DEC's Alpha: אם ההגדרה של precise exceptions לא מתקיימת (למשל: debugging) – לא יודעים איך קרה, קשה לעשות - overflow

oוגי ה-exceptions שעשויים להיות ב-exceptions

| Pipeline Stage | Possible Exception                                                             |

|----------------|--------------------------------------------------------------------------------|

| IF             | Page fault on fetch =                                                          |

|                | כשצריך להביא קטע מהתוכנית לזיכרון כשצריך אותו, אבל הוא עדיין לא שם.            |

|                | Segmentation fault = גישה למקום שאין דף עבורו                                  |

|                | Memory protection = execute only שהוא text למשל, ניסיון לקרוא                  |

| ID             | Undefined or illegal op-code.                                                  |

|                | בקריאה של האוגרים עצמם אין exceptions. יש exceptions אם ה-op-code הוא לא חוקי. |

| EX             | Arithmetic exception.                                                          |

| MEM            | Page fault on data                                                             |

|                | Segmentation fault                                                             |

|                | Memory protection                                                              |

| WB             | None.                                                                          |

# <u>עמ' 4-4 - שיעור 5:</u>

# :Loop Unrolling

ניתן להשתמש ב-unrolling עמ"נ להגדיל את המספר הממוצע של הפקודות המבוצעות בפעימת שעון אחת. הרעיון ב-loop unrolling: משכפלים את גוף הלולאה מספר פעמים במטרה להקטין את האחוז של מספר הרעיון ב-loop unrolling: מכף מספקים יותר מרחב לתזוזה של יחידות הקוד עמ"נ להיפטר מ-stalls בהם לא עושים כלום.

ע"י loop unrolling ניתן למצוא יותר אפשרויות למקביליות (טוב ל-pipeline).

## :Instruction Level Parallelism :6

אם ברצוננו לבצע קוד מכונה באופן סדרתי ומהיר צריך לנסות למצוא פקודות שיכולות להתבצע בלי dependencies ניתן לנסות גם לבצע פקודות מסוימות סימולנטית (במקביל). אולם צריך לשים לב ל-dependencies בין הפקודות שמונעות מכמה פקודות להתבצע במקביל.

# קיימים 3 סוגי תלויות שמפריעות ל-ILP:

- בפקודה i אם אחד מהתנאים הבאים data dependent פקודה j פקודה:  $Data \ Dependencies$

- א. פקודה i מפיקה תוצאה שפקודה j משתמשת בה.

- .i בפקודה data dependent בפקודה k, ופקודה k בפקודה data dependent בפקודה בפקודה

- 2. Name Dependencies: כאשר 2 פקודות משתמשות באותו אוגר או באותו מקום בזיכרון (name), אבל אין: (flow of data). זרימת נתונים

- ע"י register rewriting משנים שמות אוגרים ש"מתו" כך שניתן לבצע דברים במקביל.

- 3. מלוי, יש. branch באופן. בהתאם לפקודת התאם לפקודת בקרה קובעת את סדר הפקודות בהתאם לפקודת. לשמור על תלויות של בקרה.

# :Basic Dynamic Branch Prediction

ככל שרוצים לנצל יותר ILP, כך תלויות הבקרה מהוות גורם מעכב יותר ויותר. לרוב פקודה אחת מתוך 6 פקודות היא פקודת branch.

שיטת ה-dynamic branch prediction buffer הפשוטה ביותר היא dynamic branch prediction הפשוטה ביותר היא dynamic branch של הפקודה. הזיכרון table של הפקודה. הזיכרון קטן שהאינדקסים בו הם הביטים התחתונים של כתובת ה-branch של הפקודה. הזיכרון מכיל ביט שמציין האם ה-branch הזה בוצע לאחרונה או לא. אם נאחסן יותר ביטים ניתן לקבל חיזוי יותר טוב. ברוב המעבדים כיום מאחסנים כ-4-3 ביטים.

ה-branch target buffer משמש לשמור את הכתובת של ה-branch כדי שלא תהיה השהייה בשביל החישוב כל פעם.

# <u>עמ' 3-2 - שיעור 6: Bill שיעור 3-2 שיעור 3-</u>

#### :Superscalar

במקום לקרוא 32 ביט קוראים 64 ביט.

בכל פעימת שעון מכניסים **2 פקודות** ל-pipeline ומנסים לבצע אותן – קל למתכנת, קשה למכונה.

ב-superscalar ניתן לקחת קוד כתוב ולבצע את זה ללא שינוי בתוכנה (ע"י מציאת פקודות בלתי תלויות וביצוען) ב-superscalar ניתן לקחת קוד כתוב ולבצע את זה ללא שינוי בתוכנה (ע"י מציאת פקודות בלתי תלויות וביצוען) ב-mplicit parallelism  $\leftarrow$

.המהדר עושה את זה: VLIW (Very Large Instruction Word)

לוקח פקודה ארוכה (למשל: 128 ביטים), מחלק את הפקודה לשדות ומבצע את הפקודה ← צריך מהדר חדש או מהדר שיודע לעשות אופטימיזציה ויודע מה ניתן לבצע במקביל – explicit parallelism.

. מקביליות = מקביליות בבת אחת בבת אחת בשניהם ← 1 קטן מ-1

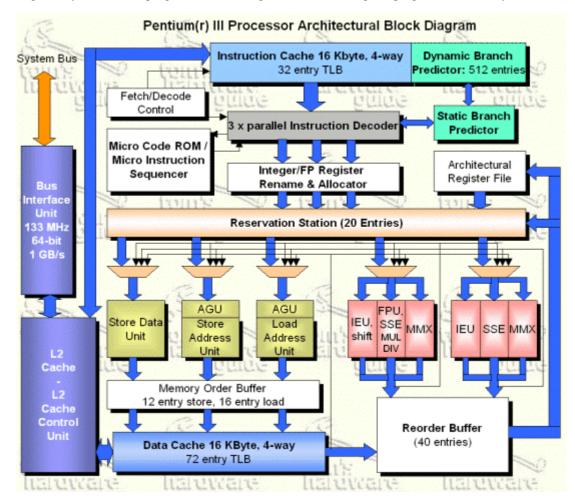

# <u>:Pentium Pro - מאמר ראשון</u>

The goal: exceed the performance of the 100MHz Pentium processor.

The Pentium processor's pipelined implementation uses 5 stages to extract high throughput. The Pentium Pro processor moves to a decoupled, 12-stage, superpipelined implementation, trading less work per pipestage for more stages (Pentium 4 is 20-stage pipelined). The Pentium Pro processor reduced its pipestage time by 33%, compared with a Pentium processor, which means the Pentium Pro processor can have a 33% higher clock speed than a Pentium processor.

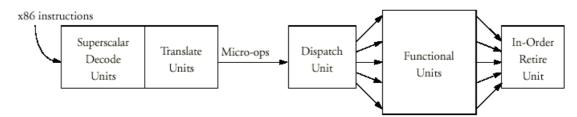

The Pentium processor's superscalar microarchitecture has an ability to execute 2 instructions per clock. The new approach used by Pentium Pro processor removes the constraint of linear instruction sequencing between the traditional "fetch" and "execute" phases, and opens up a wide instruction window using an instruction pool. This approach allows the "execute" phase of the Pentium Pro processor to have much more visibility into the program's instruction stream so that better scheduling may take place. It requires the instruction "fetch/decode" phase of the Pentium Pro processor to be much more intelligent in terms of predicting program flow. Optimized scheduling requires the fundamental "execute" phase to be replaced by decoupled "dispatch/execute" and "retire" phases. This allows instructions to be started in any order but always be completed in the original program order.

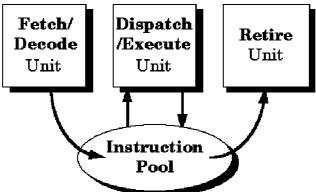

The Pentium Pro processor is implemented as 3 independent engines that communicate using an instruction pool:

Figure 1. The P6 is implemented as three independent engines that communicate using an instruction pool.

### What is the fundamental problem to solve?

### Example:

$r1 \leftarrow mem[r0]$

$r2 \leftarrow r1 + r2$

$r5 \leftarrow r5 + 1$

$r6 \leftarrow r6 - r3$

The 1<sup>st</sup> instruction causes cache miss. The CPU stalls while waiting for the data → under-utilized. To avoid this memory latency problem the Pentium Pro processor "looks-ahead" into its instruction pool at subsequent instructions and will do useful work rather than be stalled. In the above example, instruction 2 will not be executed since it depends upon the result of instruction 1. However, both instructions 3 and 4 can be executed. Since we must maintain the original program order, the results of instructions 3 and 4 are stored back in the instruction pool awaiting in-order retirement → Instructions are executed out of order.

Dynamic Execution technology can be summarized as optimally adjusting instruction execution by predicting program flow, analyzing the program's dataflow graph to choose the best order to execute the instructions, then having the ability to speculatively execute instructions in the preferred order.

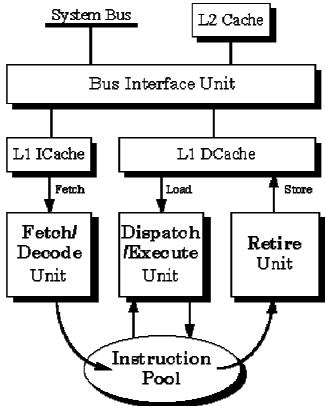

The Pentium Pro processor pipeline:

- Fetch/Decode Unit: An in-order unit that takes as input the user program instruction stream from the instruction cache and decodes them into a series of micro-operations that represent the dataflow of that instruction stream. The program pre-fetch is itself speculative.

- *Dispatch/Execute unit*: An out-of-order unit that accepts the dataflow stream, schedules execution of the micro-operations s.t. data dependencies and resource availability and temporarily stores the results of these speculative executions.

- *Retire unit*: An in-order unit that knows how and when to commit ("retire") the temporary, speculative results to permanent architectural state.

- Bus Interface unit: A partially ordered unit responsible for connecting the 3 internal units to the real world.

Figure 3. The three core engines interface with the memory subsystem using 8K/8K unified caches.

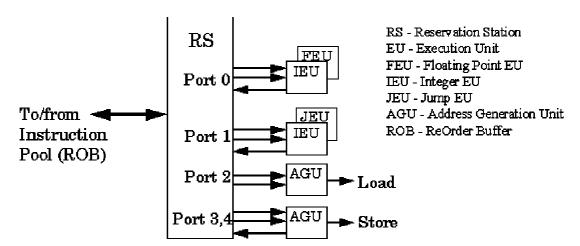

Figure 5: Looking inside the Dispatch/Execute Unit

Figure 4: Looking inside the Fetch/Decode Unit

Pool (ROB)

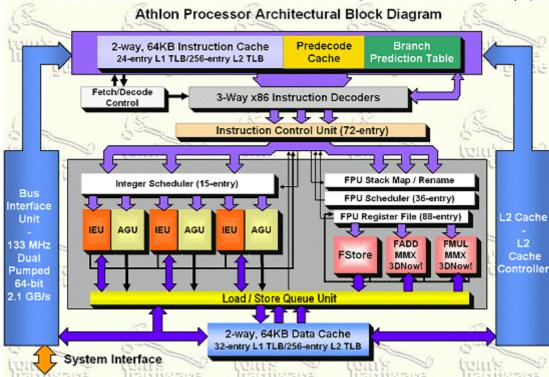

### :Pentium 4 – מאמר שני

**Processor Architecture** refers to the instruction set, registers and memory-resident data structures. **Processor Micro-architecture** refers to implementation of a processor architecture in silicon.

What determines true processor performance?

Performance = MHz x IPC

Performance can be improved by increasing frequency, IPC or optimally both. Frequency is a function of both the manufacturing process and the micro-architecture. At a given clock frequency, the IPC is a function of processor micro-architecture and the specific application being executed. Increasing either frequency or IPC and holding the other close to constant with the prior generation can still achieve a significantly higher level of performance.

It is also possible to increase performance by reducing the number of instructions that it takes to execute the specific task being measured (Single Instruction Multiple Data).

**Integer and basic office productivity applications** tend to have many branches in the code that are difficult to predict, thus reducing overall IPC potential.

**Floating point and multimedia applications** tend to have branches that are very predictable and thus naturally have a higher average IPC potential.

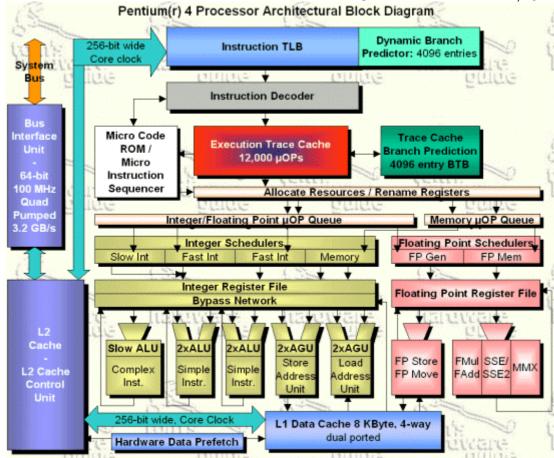

The Pentium 4 processor uses out-of-order speculative execution and superscalar execution. In Pentium 4 processor a **hyper-pipelined technology** (20-stage) was implemented, where the depth of the pipeline was doubled from that of the P6 micro-architectural generation (Pentium 3). This deeper pipeline delivers significantly higher levels of frequency. The design effort focused on the following:

- Minimizing the penalty associated with branchmis-predicts:

- The micro-architecture takes advantage of out-of-order, speculative execution. This is where the processor routinely uses an internal branch prediction algorithm to predict the result of branches in the program code and then speculatively executes instructions down the predicted code branch. If the processer mis-predicts a branch, all the speculatively executed instructions must be flushed from the processor pipeline in order to restart the instruction execution down the correct program branch. On more deeply pipelined designs, more instructions must be flushed from the pipeline, resulting in a longer recovery time from a branch mis-predict  $\rightarrow$  applications that have many, difficult to predict, branches will tend to have a lower average IPC.

- Keeping the high frequency execution units busy (vs. sitting idle)

- Reducing the number of instructions needed to complete a task or program

Many applications often perform repetitive operations on large sets of data. Further, the data sets involved in these operations tend to be small values that can be represented with a small number of bits. These two observations can be combined to improve application performance by both compactly representing data sets and by implementing instructions that can operate in these compact data sets (Single Instruction Multiple Data) → reducing the overall number of instructions that a program is required to execute.

Using Advanced Dynamic Execution (as in the previous article).

**BTB** – Branch target buffer: In this table you can find all the addresses to where a branch will or could be made.

AGU – Address generation unit: This unit is responsible for the data from or to the correct address to either be loaded or stored. Absolute addressing in programs is only used in rare exceptions. As soon as you've got arrays of data the program code is using indirect addressing, keeping the 'AGUs' busy.

Pentium 3 has 10-stage pipeline, Athlon has 11, and Pentium 4 has 20.

The reason for the longer pipeline is Intel's wish of Pentium 4 to deliver highest clock rates. The smaller or shorter each pipeline stage, the fewer transistors or 'gates' it needs and the faster it is able to run. However, there is also one big disadvantage to long pipelines. As soon as it turns out at the end of the pipeline that the software will branch to an address that was not predicted, the whole pipeline needs to be flushed and refilled. The longer the pipeline the more 'in-flight' instructions will be lost and the longer it takes until the pipeline is filled again.

Pentium 4 pipeline can keep up to 126 instructions 'in-flight', amongst them up to 48 load and 24 store operations. The improved trace cache branch prediction unit described above is supposed to ensure that flushes of this long pipeline are only rare occasions.

The stuff that happens in the trace cache, as mentioned above, only represents the first five stages of the pipeline of Pentium 4. What follows is:

- Allocate resources

- Register renaming

- Write into the μOP queue

- Write into the schedulers and compute dependencies

- Dispatch μOPs to their execution units

- Read register file (to ensure that the correct ones of the 128 all-purpose register files are used as the register(s) for the actual instruction)

After that comes the actual execution of the μOP.

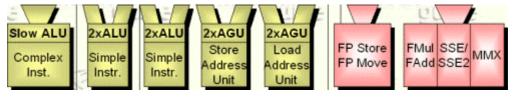

### The Rapid Execution Engine:

The basic parts of the 'Rapid Execution Engine' are the two 'double-pumped' ALUs and AGUs. Each of the four is said to be clocked with double the processors clock, because they can receive a  $\mu$ OP every half clock. Simple  $\mu$ OPs that can be processed by the Rapid Execution Engine are executed in half a clock, which is obviously a very good thing.

The story looks a lot different for the instructions that cannot be processed by the rapid execution units. Those instructions or  $\mu$ OPs need to use the one and only 'Slow ALU', which is not 'double pumped'. The majority of instructions need to use this path. However, the majority of code actually consists of

the most simple 'AND', 'OR', 'XOR', 'ADD', .... instructions, making Intel's 'Rapid Execution Engine'-design sensible though not particularly amazing.

Things look worse if you have a look at the red boxes, which represent the FPU-part of Pentium 4.

# SSE2 - The New Double Precision Streaming SIMD Extensions

To conclude this epic piece about Pentium 4's internal architecture I need not forget to mention SSE2. 144 new instructions are finally enabling everything that SSE was expected to be in the first place. The 128-bit of packed data, which could only be in form of four single-precision floating-point values under SSE can now be operated in all of the following options:

- 4 single precision FP values (SSE)

- 2 double precision FP values (SSE2)

- 16 byte values (SSE2)

- 8 word values (SSE2)

- 4 double word values (SSE2)

- 2 quad word values (SSE2)

- 1 128-bit integer value (SSE2)

The options are vast and the usefulness undoubted.

| Feature                                  | AMD Athlon <sup>TM</sup><br>Processor | Pentium® III        | Pentium® 4                     |

|------------------------------------------|---------------------------------------|---------------------|--------------------------------|

| Operations per clock cycle               | 9                                     | 5                   | 6                              |

| Integer pipelines                        | 3                                     | 2                   | 4                              |

| Floating point pipelines                 | 3                                     | 1                   | 2                              |

| Full x86 decoders                        | 3                                     | 1                   | 1                              |

| L1 cache size                            | 128KB                                 | 32KB                | 12k μop + 8KB Data Cache       |

| L2 cache size                            | 256KB on-chip                         | 256KB on-chip       | 256KB on-chip                  |

| Total on-chip full-speed cache           | 384KB                                 | 288KB               | 264KB + 12k μop                |

| Total effective on-chip full-speed cache | 384KB<br>(exclusive)                  | 256KB (inclusive)   | 256KB - 12k μop<br>(inclusive) |

| System bus speed                         | 200 MHz to<br>266MHz                  | 100MHz or<br>133MHz | 400MHz                         |

| 3D enhancement instructions              | Enhanced 3DNow! <sup>TM</sup>         | SSE                 | SSE2                           |

| Single-precision FP SIMD                 | Yes                                   | Yes                 | Yes                            |

| 4 FP operations per clock                | Yes                                   | Yes                 | Yes                            |

| Cache/prefetch controls                  | Yes                                   | Yes                 | Yes                            |

| Streaming controls                       | Yes                                   | Yes                 | Yes                            |

| DSP/comm extensions                      | Yes                                   | No                  | Yes                            |

| ROB                                      | 72                                    | 42                  | 126                            |

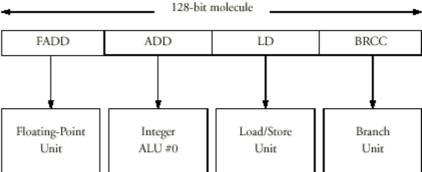

### Crusoe - Transmeta :מאמר שלישי

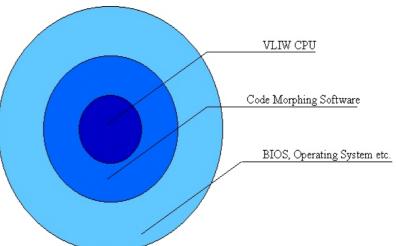

The Crusoe processor solutions consist of a hardware engine logically surrounded by a software layer. The engine is a very long instruction word (VLIW) CPU capable of executing up to 4 operations in each clock cycle. It has been designed purely for fast low-power implementation using conventional CMOS fabrication. The software layer is called Code Morphing software because it dynamically "morphs" x86 instructions into VLIW instructions. In other words, the Transmeta designers have judiciously rendered some functions in hardware and some in software, according to the product design goals and constraints.

The Transmeta designers have decoupled the x86 instruction set architecture from the underlying processor hardware, which allows this hardware to be very different from a conventional x86 implementation. For the same reason, the underlying hardware can be changed radically without affecting legacy x86 software: each new CPU design only requires a new version of the Code Morphing software to translate x86 instructions to the new CPU's native instruction set.

The Code Morphing software offers opportunities to improve performance without altering the underlying hardware.

Transmeta created a very simple, high performance, VLIW engine with 2 integer units, a floating point unit, a memory (load/store) unit and a branch unit. A Crusoe processor long instruction word, called a *molecule*, can be 64 bits or 128 bits long and contain up to 4 RISC-like instructions, called *atoms*. All atoms within a molecule are executed in parallel, and the molecule format directly determines how atoms get routed to functional units. Molecules are executed in order, so there is no complex out-of-order hardware. To keep the processor running at full speed, molecules are packed as fully as possible with atoms.

Figure 1. A molecule can contain up to four atoms, which are executed in parallel.

Superscalar out-of-order x86 processors, such as the Pentium 2 and Pentium 3 processors, also have multiple functional units that can execute RISC-like operations (micro-ops) in parallel. The hardware these designs use to translate x86 instructions into micro-ops and schedule (dispatch) the micro-ops to make best use of the functional units:

Figure 2. Conventional superscalar out-of-order CPUs use hardware to create and dispatch micro-ops that can execute in parallel.

Since the dispatch unit reorders the micro-ops as required to keep the functional units busy, a separate piece of hardware, the in-order retire unit, is needed to effectively reconstruct the order of the original x86 instructions, and ensure that they take effect in proper order.

# **Code Morphing Software**

The code morphing software's function is to translate instructions from one instruction set architecture (x86 target ISA) into instructions for the VLIW engine that the Crusoe processor uses. The code morphing software is the only piece of software that is written into the Crusoe processors Code Morphing component. The Code Morphing software resides in a 512kb flash chip and this is the first thing to be loaded. The code morphing software can translate an entire batch of x86 instructions at once, the resulting translation is stored into a translation cache. Once translated an instruction does not have to be translate again. The Crusoe translation cache, including the code morphing code, is in a separate memory area that is inaccessible to x86 code. At initialization time the code morphing software copies itself from ROM to DRAM because of faster access times when in DRAM compared to ROM.

As with most caching techniques, the code morphing software takes advantage of "locality reference." It does this by reusing translated instructions that already reside within its translation cache. When a translation is made the processor does not know how much of the translated code will be of use to it. Most frequently executed code has to be given priority over, say, an instruction that is only executed once. The code morphing software has a number of different modes that it can use to get the best translation

results. These modes include interpretation (slow, but has no translation overhead) through translation with straightforward code generation, all the way to vastly optimized code. This type takes the longest to generate, but runs faster. Feedback from the code morphing software determines the type of translation mode that will be used. Code Morphing Software collects data from previous executions of instructions and uses this history to predict future execution patterns and prepare for them. Code information such as block execution frequencies and branch history is calculated. This data is used to decide what to optimize and translate.

The flexibility of the software translation approach comes at a price: the processor has to dedicate some of its cycles to running the Code Morphing software, cycles that a conventional x86 processor could use to execute application code.

# Decoding and Scheduling:

Conventional x86 superscalar processors fetch x86 binary instructions from memory and decode them into micro-operations, which are then reordered by out-of-order dispatch hardware and fed to the functional units for parallel execution.

In contrast, Code Morphing can translate an entire group of x86 instructions at once, creating a *translation*, whereas a superscalar x86 translates single instructions in isolation. Moreover, while a traditional x86 translates each x86 instruction every time it is executed, Transmeta's software translates instructions *once*, saving the resulting translation in a *translation cache*. The next time the (now translated) x86 code is executed, the system skips the translation step and directly executes the existing translated code.

#### Caching:

The translation cache, along with the Code Morphing code, resides in a separate memory space that is inaccessible to x86 code. The Code Morphing software's technique of reusing translations takes advantage of "locality of reference". As an application executes, Code Morphing "learns" more about the program and improves it so it will execute faster and faster.

<u>Filtering:</u> (idea: code that the program executes very often should be optimized as best as can be) In typical applications, a very small fraction of the application's code (often less than 10%) accounts for more than 95% of execution time. Therefore, the translation system needs to choose carefully how much effort to spend on translating and optimizing a given piece of x86 code. The Code Morphing software includes in its arsenal a wide choice of execution modes for x86 code, ranging from

interpretation (which has no translation overhead at all, but executes x86 code more slowly), through translation using very simple-minded code generation, all the way to highly optimized code (which takes longest to generate, but which runs fastest once translated).

# **<u>Prediction and path selection:</u>** (idea: statistics by branch)

The translator adds code whose sole purpose is to collect information such as block execution frequencies, or branch history. This data can be later used to decide when and what to optimize and translate. For example, if a given conditional x86 branch is highly biased (e.g., usually taken), the system can likewise bias its optimizations to favor the most frequently taken path. Alternatively, for more balanced branches (taken as often as not, for example), the translator can decide to speculatively execute code from both paths and select the correct result later. Analogously, knowing how often a piece of x86 code is executed helps decide how much to try to optimize that code.

#### Example:

```

A. addl %eax, (%esp) // load data from stack, add to %eax

B. addl %ebx, (%esp) // load data from stack, add to %ebx

C. movl %esi, (%ebp) // load %esi from memory

D. subl %ecx, 5 // subtract 5 from %ecx

```

*First:* translating the x86 instructions to simple sequence of atoms:

```

A ld %r30, [%esp] // load from stack, into temporary

A add.c %eax, %eax, %r30 // add to %eax, set condition codes.

B ld %r31, [%esp]

B add.c %ebx, %ebx, %r31

C ld %esi, [%ebp]

D sub.c %ecx, %ecx, 5

```

**Second:** the optimizer applies well-known compiler optimizations to the code, such as: (a) common subexpression elimination, (b) loop invariant removal, or (c) dead code elimination:

**Third:** the scheduler reorders the remaining atoms and groups them into individual molecules. This process is similar to what out-of-order processors do in their dispatch hardware:

```

1. ld %r30, [%esp]; sub.c %ecx, %ecx, 5

2. ld %esi, [%ebp]; add %eax, %eax, %r30; add %ebx, %ebx, %r30

```

# 2 important points to observe:

- Though the molecules are executed in-order by the hardware, they perform the work of the original x86 instructions out of order.

- The molecule explicitly encode the instruction level parallelism, hence they can be executed by a simple VLIW engine.

#### **Exceptions and speculation:**

In the x86 ISA, exceptions are *precise*: when one instruction causes an exception, all instructions preceding it must complete before the exception is reported and none of the subsequent instructions may complete. In the translation the ordering of the instructions might be different thus we might already execute code and by that to violate the rules of the precise exceptions. Out-of-order processors also have this problem. They employ complex hardware mechanisms to delay or undo the effects of micro-ops that have been executed "too soon".

**The Crusoe solution:** all registers holding x86 state are **shadowed**, i.e. there exists 2 copies of each register, a **working** and a **shadow** copy. Normal atoms only update the working copy of the register. When execution reaches the end of a translation without encountering an exception, a special **commit** operation copies all working registers into their corresponding shadow registers. If any x86-level exception occurs inside the translation, the runtime system undoes the effects of all molecules executed since the start of the translation. This is done via a **rollback** operation which copies the shadow register

values back into the working registers. At this point, the Code Morphing software re-executes the x86 instructions conservatively, i.e. in their original program order, to determine the actual location of the exception.

# Alias hardware:

When the translator moves a load operation ahead of store operation, it converts the load into a load-and-protect and the store into a store-under-alias-mask. In the unlikely event that the store operation overwrites the previously loaded data, the processor raises an exception and the runtime system can take corrective action. Using this mechanism it is always safe to reorder memory loads and stores. The alias hardware can also help eliminating redundant load/store atoms.

#### LongRun power management:

Adjusting the power consumption without turning the processor off by adjusting the clock frequency on the fly. The Code Morphing can also adjust the Crusoe processor's voltage on the fly (since at a lower operating frequency, a lower voltage can be used).

Example: If we need only 200MHz out of the 700MHz we have, then we decrease the clock (instead of 700 to 200) and now, since we're working on a lower clock  $\rightarrow$  we can decrease the voltage (P = KCV<sup>2</sup>, whereas P = the chip's power [הספק], C = clock [MHz], V = voltage

Note: Crusoe processor is efficient in caching: we divide the code to blocks and put the blocks in the cache. Every time we get to a block already translated, we jump to the code. Since it is done in the software we can take a bigger window to optimize.

# Advantages of the Code Morphing software:

The Code Morphing software provides the Crusoe processor with unprecedented flexibility by implementing the complexities of a traditional microprocessor in software. This results in the following advantages over conventional x86 processors:

| Traditional x86 Processors                 | Crusoe Processor with Code Morphing software                      |  |  |  |

|--------------------------------------------|-------------------------------------------------------------------|--|--|--|

| Translates single instructions one at time | Translates an entire group of x86 instructions at once            |  |  |  |

| Translates each x86 instruction every time | Translates instructions once, saving the resultant translation in |  |  |  |

| it is encountered                          | a cache for re-use                                                |  |  |  |

| Full of complex, power-hungry transistors  | Much of the processor functionality is implemented in             |  |  |  |

| run of complex, power-nungry transistors   | software — less logic transistors, less power                     |  |  |  |

### בעוי: Understanding the IA-64 Architecture: מאמר רביעי

## **Today's architecture challenges:**

- Sequential semantics of the ISA

- Low instruction level parallelism (ILP)

- Unpredictable branches, memory dependencies

- Ever increasing memory latency

- Limited resources (registers, memory addresses)

- Procedure call, loop pipelining overhead.

### **IA-64 overcomes these challenges:**

- Sequentially inherent in traditional architecture.

- Complex hardware needed to (re)extract ILP.

- Limited ILP available within basic blocks.

- Branches make extracting ILP difficult.

- Memory dependencies further limit ILP.

# Sequential semantics – The problem:

A program is a sequence of instructions. There's implied order for the execution of the instructions and potential dependence from instruction to instruction. However, high performance needs parallel execution and parallel execution needs *independent* instructions, thus: independent instructions must be (re)discovered.

The compiler knows the available parallelism, but has no "vocabulary" to express it  $\rightarrow$  Hardware must (re)discover parallelism (= complex hardware needed to (re)extract ILP).

#### *In IA-64:*

Program is a sequence of *parallel* instructions groups. There's implied order of instructions groups. There's *no* dependence between instructions within the group  $\rightarrow$  independent instructions are explicitly indicated.

The compiler knows the available parallelism, and now *has* the "vocabulary" to express it  $\rightarrow$  Hardware easily exploits the parallelism.

# Low instructions level parallelism – The problem:

Branches – frequent; code block – small. Wider machines need more parallel instructions  $\rightarrow$  need to exploit ILP across branches.

# **Branch unpredictability - The problem:**

Branches alter the "sequence" of instructions. ILP must be extracted across branches. Branch prediction has limitations:

- Not perfect, performance penalty when wrong.

- Need to speculatively execute instructions that can fault.

- Need to defer exceptions on speculative operations → more book keeping overhead hardware.

#### *In IA-64*:

Prediction is done by transferring control flow to data flow → prediction removes/reduces branches and enables and enhances ILP.

Unpredictable branches are removed → misprediction penalties are eliminated.

ILP within the basic block increases → both "then" and "else" are executed in parallel.

Wider machines are better utilized.

Each instruction contains three 7-bit GPR register fields (128 integer + 128 floating point registers).

Register set (integer vs. floating point) is determined by instruction.

IA-64 compilers will have to be even smarter than RISC compilers:

- Must attach predicates to conditional branches to aid in speculative execution.

- Must analyze potential parallelism to set template bits appropriately.

- Must check for loads from memory and insert speculative load instruction earlier in stream and replace normal load with speculative check instruction.

IA-64 instructions are fixed length – about 40 bits long.

Instructions can be out-of-order and they can originate from different paths of a branch.

Branch prediction enables chip to execute parallel branches speculatively and discard unneeded results.

## Memory dependencies – The problem:

Loads are usually at the top of a chain of instructions. ILP extraction requires moving these loads.

# <u>Memory latency – The problem:</u>

Need to distance loads from their uses.

# Resource constraints – The problem:

- 1. Small register space → limits compilers ability to "express" parallelism and creates false dependencies (can be overcome by renaming).

- 2. Shared resources: condition flags, control registers and etc. It forces dependencies on otherwise independent instructions.

- 3. Floating point resources.

# <u>Loop optimization overhead – The problem:</u>

Loops are a common source of good ILP. Unrolling/Pipelining exploit this ILP. Prologue/Epilogue cause code expansion. Unrolling causes more code expansion and thus limits the applicability of these techniques.

#### מערכת הזיכרון:

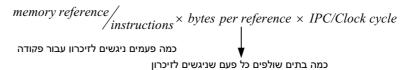

ה-CPU יכול להיות מהיר ככל שהזיכרון יאפשר. כדי שנוכל לקיים את הבקשות בלי השהיות ה-bandwidth צריך להיות:

*מקומיות בזמן (temporal locality):* אם השתמשנו ביחידת נתונים לאחרונה ← יש סיכוי גבוה שנשתמש בה שוב בקרוב. שוב בקרוב.

*מקומיות במרחב (spatial locality):* אם השתמשנו ביחידת נתונים לאחרונה ← יש סיכוי גבוה שנשתמש בנתונים שכנים (למשל: במערכים).

במבות (שומרים בלוקים שניגשנו אליהם לאחרונה) ומקומיות זמנית (שומרים בלוקים שניגשנו אליהם לאחרונה) ומקומיות cache מבחבית (חלוקת הזיכרון לבלוקים). ניהול ה-cache

מחלקים את הזיכרון לבלוקים של 16 או 32 בתים. בתוך ה-cache שמים יחידות של בלוקים מלאים (יש state, address tag and data שבו יש block frame. את הבלוקים שמים ב-block frame

את ה-address tag מחלקים ל-2:

- .block מאפיין את ה-tag .1

- .block המיקום בתוך ה-offset

.hit – שצריך נמצא כבר tag-בעת גישה לזיכרון בודקים: אם ה

:אחרת – miss – אחרת

- 1. מחליפים בלוק ישן.

- 2. מקבלים את הבלוק החדש מהזיכרון.

- .cache שמים את הבלוק ב-3

- 4. מחזירים את המילה הנחוצה מהבלוק.

בתים. במה: יש לנו cache block frame בגודל

lw \$4, 0x128

אם אזי מקבלים את (0x128 mod 16 = 0x128 & 0xfffffff0) cache-בודקים אם 0x120 tag בודקים אם :block

state tag data

valid 0x120 oxffffffff, 0x1, 0x7, 0x3

.\$4- ומאחסנים אותו סx7 את CPU- ולכן מחזירים ל-offset והוא ה-offset התו הימני ביותר

lw \$5, 0x124

.CPU-ט 0x1 נמצא ב-cache? כן, ולכן מחזירים ישר את 0x120 tag בודקים אם

# mean access = cache access + miss ratio \* main memory access

50) אחד. לעומת זאת בלי cache דורש cache דורש cycle דורש cache דורש cache דורש cache דוגמה: אם לקיחת נתון מה-cache דורש cache דורש cache דורש cache באחד. אחד מהמקרים צריך לגשת לזיכרון אזי: 0.1 = 0.01 \* 50 = 1.5 ובאחוז אחד מהמקרים צריך לגשת לזיכרון אזי:

### <u>הגדרות:</u>

היחידה המינימלית שניתן לייצג. – block

.cache-הבלוק נמצא - *hit*

.(working set > cache size) cache - הבלוק לא נמצא ב – miss

miss - אחוז הגישות שגורמות ל- miss ratio

.cache-זמן גישה ל – hit time

.CPU- הזמן שלוקח + cache הבלוק בלוק ב-miss penalty

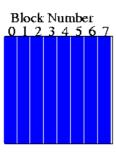

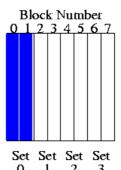

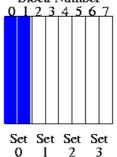

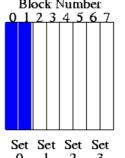

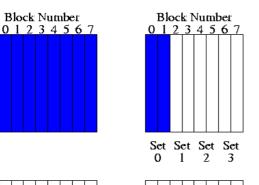

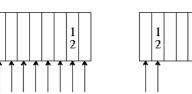

### :Block Placement

- שהאינדקס b ו-a שהאינדקס הבלוק יכול להיות בכל frame הבלוק יכול להיות בכל fully associative שלהם זהה, הם תמיד יכולים להישאר ב-cache בלי להפריע אחד לשני. *חסרון:* כל פעם צריך לחפש במקביל.

- לוד הבלוק נכנס ל-frame אחד בלבד: אם אני קורא b ו-d שהאינדקס שלהם זהה, אזי מוריל frame. אני כל הזמן עושה החלפה ביניהם.

- .set associative הבלוק נכנס לקבוצה אחת בלבד.

Block Number

<u>דוגמה:</u> לאן ילך בלוק 12 (1100)?

Direct Mapped

1) Fully Associative

| tag (block #) | offset |

|---------------|--------|

2) Set Associative

:fully associative

:set associative

:direct mapped

$0xa12 \rightarrow tag = block \# = a1, offset = 2.$

| tag | index | offset |

|-----|-------|--------|

כל אינדקס יכול להיות רק בקבוצה אחת. יש כאן 4 קבוצות ולכן גודל האינדקס יהיה 2.

| tag index offset |

|------------------|

|------------------|

Block Number

2

3) Direct Mapped

.cache a מגיע למקום ספציפי. ה-index בוחר את המקום בתוך ה-cache cache בדוגמה הנ"ל האינדקס יהיה בעל 3 ביטים וה-tag והאינדקס מהווים את ה-# block .

$0xa12 \rightarrow a1 = 10100 \ 001 \rightarrow tag = block \# = a1 = 20, offset = 2, index = 1$

# ?cache-איך מוצאים בלוק ב

- השוואת ה-tag.

- חיפוש מקבילי למציאת lookup.

- בדיקת ה-valid bit.

<u>דוגמה:</u> איך נמצא את בלוק 12?

ב-fully associative הבלוק יכול להימצא בכל כתובת ואנחנו רוצים למצוא אותו בפעימת שעון אחת + צריך יותר חומרה (כדי לאפשר בדיקה במקביל) ← צריך זיכרון אסוציאטיבי.

ב-direct mapped מסתכלים על 3 הביטים הנמוכים ביותר של 12 ומקבלים  $.(12 = 1\ 100)\ 4$

1) Fully Associative

### איזה בלוק מחליפים כתוצאה מ-miss?

- אופטימלי למקומיות זמנית. LRU 1

- 2. רנדומלי כמעט טוב כמו LRU. פשוט יותר.

- יובוחרים באופן תנדומי most recently used עוקבים אחרי NMRU Not Most Recently Used .3 מהאחרים.

- 4. (offline) מחליפים את הבלוק שבו נשתמש עוד פעם הכי מאוחר (Belady's Algorithm).

### :miss-סוגי ה

- .cache בגישה הראשונה לבלוק. זהה לכל סוגי ה-(miss in infinite cache). בגישה הראשונה לבלוק.

- .2 אינו מספיק גדול. cache- קורה כאשר ה-*(miss in fully associative cache =) capacity*

- 2 שיש fully associative שאינו cache יכול להיות שיש: למשל: עבור conflict .3 .conflict misses שהיעים לאותו אינדקס. הגדלת אסוצ' ← אסונת working set שמגיעים לאותו אינדקס.

- .4 cocherence .4 ממעבדים אחרים (כאשר יש זיכרון משותף לכמה מעבדים). פתרון: bus ממעבדים הזיכרון הוא על bus משותף. ברגע שנכתב ערך לכתובת שנמצאת ב-memory snooping המחשב השני, המחשב השני מאזין לפס, רואה את זה ולכן בגישה הבאה שלו לכתובת הזו הוא יבטל את snooping טוב ל-cache ויביא אותו חזרה מהזיכרון. ה-snooping טוב ל-cache ויביא אותו חזרה מהזיכרון.

## :cache-גודל

בודל ה-cache הוא גודל אחסון הנתונים (לא כולל ה-cache הוא גודל אחסון הנתונים (לא כולל ה-

- גודל גדול יותר יכול לנצל מקומיות זמן טוב יותר.

- גודל גדול יותר זה *לא תמיד טוב יותר*.

. גדול מדי ← איטי יותר; זמן גישה עשוי להיות גרוע במסלולים קריטיים. Cache

תור מדי לא מנצל מקומיות זמן טוב; מידע חשוב מוחלף יותר מדי מוקדם. ← לא מנצל מקומיות ל

.tag overhead גודל הטו מדי  $\rightarrow$  לא מנצלים טוב מקומיות מרחבית: יש *iblock size*

גודל גדול מדי ← יש העברות מידע לא נחוצות; מידע נחוץ מוחלף מוקדם מדי עקב זה שיש מספר כולל של בלוקים קטן.

miss rate פחות :larger associativity :Associativity

smaller associativity: עלות נמוכה יותר; בד"כ

ב-set associative cache אבל זמן הגישה האפקטיבי גרוע direct mapped cache לעומת set associative cache יש פחות יותר.

tag-אולם הכתיבות לא נעשות כך ולכן הכתיבות איטיות וtag-איטיות במקביל עם השוואת במקביל עם השוואת ה-*Write Policies*

?כאשר יש hit, האם מעדכנים את הזיכרון

.write-through (store-through)  $\leftarrow$  p

.write-back (store-in, copy-back) ← לא

?cache מקצים בלוק ב-misses

.write-allocate (usually with write-back)  $\leftarrow$   $\triangleright$

.no-write-allocate (usually with write-through) ← לא

### :Write back

- עדכון הזיכרון רק כשמחליפים בלוק.

- משתמשים ב-dirty bit, כך שבלוקים נקיים מוחלפים ללא עדכון מהזיכרון.

- $.traffic/reference = f_{dirty} x miss x B$

- יש פחות traffic ל-caches

. בלבד cache-יעיל יותר מ-write through יעיל יותר מ-write back

#### :Write through

- עדכון הזיכרון בכל כתיבה.

- שמירת הזיכרון מעודכן.

- $.traffic/reference = f_{writes}$  •

- .cache של ה-performance של ה-

לפתרון בעיות coherence של הזיכרון כותבים לזיכרון. ה-cache יותר אפקטיבי לקריאות ולא לכתיבות. הכתיבה לפתרון בעיות cycles של הזיכרון כותבים לזיכרון. ה-cache לזיכרון לוקחת הרבה